(openPR) Jena; Las Vegas NV – Anlässlich der Fachmesse APEX gibt GÖPEL electronic, weltweit führender Hersteller von JTAG/Boundary Scan Lösungen gemäß IEEE1149.x, gibt unter dem Namen CION Module™/SO-DIMM204-3 die Markt¬einführung eines weiteren I/O Moduls im Rahmen der CION Modulfamilie bekannt.

Das neue digitale low-cost Modul wird über die TAP (Test Access Ports) seriell angesteuert und ermöglicht den Test sämtlicher Signal- und Spannungsversorgungspins von SO-DIMM204 Sockeln für DDR3-SDRAM kompatibel zu den JEDEC-Standards JESD21-C und JESD79-3C.

„Immer mehr Anwender setzen die modernen DDR3 Standards in ihren Produkten ein und für derartige Interfaces bieten wir jetzt eine effiziente Lösung zum tiefen strukturellen Test“, freut sich Heiko Ehrenberg General Manager US Operations bei GÖPEL electronic. „Damit bauen wir das breite Produktspektrum der CION-Modulfamilie zum Test von digitalen, analogen und Mixed-Signal Interfaces gezielt noch weiter aus“.

Das CION Module™/SO-DIMM204-3 ist bereits das 14. Modul in der Familie von CION Modulen und mechanisch kompatibel zum JEDEC Standard MO268. Es kann deshalb direkt in den zu testenden Sockel eingesteckt werden, wobei die Spannungsanpassung der Interfacestufen automatisch erfolgt. Da die Module mit transparenten TAP ausgerüstet sind, besteht die Möglichkeit mehrere Boards gleichen oder unterschiedlichen Typs nach dem Daisy Chain Prinzip zu kaskadieren. Zur flexiblen Adaption sind beide TAP extern spannungsprogrammierbar.

Der strukturelle Test sämtlicher SO-DIMM204 Signal- und Spannungsversorgungs-Pins erfolgt durch entsprechende Boundary Scan IC, wie dem CION™ ASIC. Dabei sind alle Kanäle unabhängig als Input/Output/Tristate schaltbar.

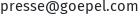

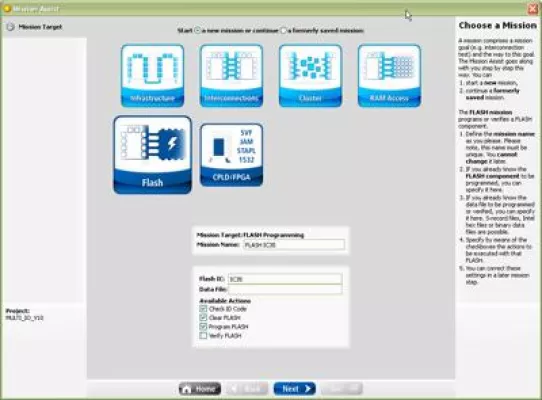

Das neue Hardware-Modul wird von allen Boundary Scan Controllern der SCANBOOSTER™- oder SCANFLEX®-Familie, sowie der integrierten Boundary Scan Softwareplattform SYSTEM CASCON™ vollständig unterstützt. SYSTEM CASCON™ ist seit mehr als 17 Jahren die innovativste Integrierte JTAG/Boundary Scan Entwicklungsumgebung und verfügt über insgesamt mehr als 40 vollständig integrierte Werkzeuge. Der Anwender kann dadurch das CION Module™/SO-DIMM204-3 komfortabel in ein entsprechendes Testprojekt integrieren, die notwendigen Testvektoren vollautomatisch generieren (ATPG), falls notwendig interaktiv debuggen und sich eventuelle Fehler auf Pin- und Netzniveau graphisch im Layout visualisieren lassen.

Presseinformation

Boundary Scan Modul erweitert strukturelle Testabdeckung auf DDR3 Speicher-Interfaces

Diese Pressemeldung wurde auf openPR veröffentlicht.

Verantwortlich für diese Pressemeldung:GÖPEL electronic GmbH

Stefan Meißner

Göschwitzer Strasse 58-66

07745 Jena

Tel.: 03641-6896-739

Fax: 03641-6896-944

E-Mail:

Internet: www.goepel.com

Stefan Meißner

Göschwitzer Strasse 58-66

07745 Jena

Tel.: 03641-6896-739

Fax: 03641-6896-944

E-Mail:

Internet: www.goepel.com

Über das Unternehmen

GÖPEL electronic ist weltweit führender Anbieter von professionellen JTAG Boundary Scan Lösungen und Technologietreiber bei IP-basierender Instrumentierung. Mit über 100 Produkteinführungen avancierte das Unternehmen in den letzten 5 Jahren kontinuierlich zum mit Abstand größten Innovator im Markt. Ein Netzwerk aus eigenen Zweigstellen, Distributoren und Servicepartnern sichert die globale Verfügbarkeit der Produkte, sowie den Support für die mehr als 7.000 Systeminstallationen. Gegründet 1991 mit Hauptsitz in Jena beschäftigt GÖPEL electronic weltweit derzeit 160 Mitarbeiter und erzielte im Jahr 2009 einen Umsatz von 17,8 Millionen Euro. Die Firma ist seit 1996 ununterbrochen ISO9001 zertifiziert und wurde im Rahmen des TOP-JOB Programms als eines der 100 besten mittelständischen Unternehmen Deutschlands ausgezeichnet. Die Produkte von GÖEPEL electronic gewannen in den letzten Jahren mehrere begehrte Auszeichnungen und werden bereits bei 5 von 10 der jeweils führenden Firmen auf den Gebieten Telekommunikation, Automotive, Luft- und Raumfahrt, Industriesteuerungen, Medizintechnik und anderen mit wachsendem Erfolg eingesetzt. Zusätzliche Informationen zum Unternehmen und seinen Produkten sind im Internet unter http://www.goepel.com zu finden.

Pressebericht „Boundary Scan Modul erweitert strukturelle Testabdeckung auf DDR3 Speicher-Interfaces“ bearbeiten oder mit dem "Super-PR-Sparpaket" stark hervorheben, zielgerichtet an Journalisten & Top50 Online-Portale verbreiten:

Disclaimer: Für den obigen Pressetext inkl. etwaiger Bilder/ Videos ist ausschließlich der im Text angegebene Kontakt verantwortlich. Der Webseitenanbieter distanziert sich ausdrücklich von den Inhalten Dritter und macht sich diese nicht zu eigen. Wenn Sie die obigen Informationen redaktionell nutzen möchten, so wenden Sie sich bitte an den obigen Pressekontakt. Bei einer Veröffentlichung bitten wir um ein Belegexemplar oder Quellenennung der URL.

Weitere Mitteilungen von GOEPEL electronic

CAN/LIN-Handbedienterminal smartCommander mit erweiterten Funktionen für die Automotive-Fertigung

Mit der neuen Version seines CAN/LIN Handbedienterminal smartCommander stellt GÖPEL electronic ein leistungsfähiges, praxisorientiertes Gerät zur Verfügung, das bezüglich seiner Einsatzmöglichkeiten weiterentwickelt wurde. smartCommander verfügt jetzt über 24 frei konfigurierbare Funktionstasten, welche unabhängig voneinander mit Botschaftssequenzen belegt, beliebig variiert, aber auch hierarchisch einander zugeordnet werden können. Das bedeutet, dass die Tasten beispielsweise auch dazu verwendet werden können, innerhalb einer gestarteten Seq…

ChipVORX-Prototyp-Instrumente für Bit Error Rate Tests (BERT)

Anlässlich der International Test Conference (ITC) zeigt GÖPEL electronic den ersten Prototypen eines ChipVORX®-Modells zur Ausführung von Bit Error Rate Tests (BERT) auf Basis von Field Programmable Gate Arrays (FPGA).

goepel.com/news/details/article/2012/11/08/goepel-electronic-demonstriert-erste-chipvorx-prototyp-instrumente-fuer-bit-error-rate-tests-bert.html

Die Lösung ermöglicht den Einsatz von FPGA Embedded Instruments in Form von speziellen Softcores zum Test und zur Design-Validierung von Highspeed-I/O. Anwender können dadurch die …

Das könnte Sie auch interessieren:

ASSET® gewinnt 2006 zum dritten Mal in Folge eine Auszeichnung beim „Best in Test“-Wettbewerb des Magazins Test & Measurement World

… Scan in einem Leiterplattendesign noch vor dem Bau eines Prototyps. Damit lassen sich teure Redesign-Durchläufe und Terminverschiebungen vermeiden, die sich oft durch unzureichende Testabdeckung beim Übergang eines Designs von der Entwicklungs- in die Fertigungsphase ergeben. Der DFT Analyzer ermittelt auch den Grad der Boundary-Scan-Testabdeckung und …

GÖPEL electronic kombiniert Boundary Scan mit Real-time Test von GBit LAN-Interfaces

GÖPEL electronic, gibt unter dem Namen BAC9305-LAN1G die Markteinführung eines weiteren Bus Access Cables (BAC) im Rahmen der revolutionären Boundary Scan Hardwareplattform SCANFLEX® bekannt. Das neue Mitglied in der Familie von Bus Access Cables ermöglicht in Verbindung mit dem SCANFLEX® Multi-Port-Bus I/O Modul SFX9305 erstmals den Real-Time Test von …

Boundary Scan Plattform SCANFLEX® erweitert Integration von Bus-Interface-Tests

GÖPEL electronic, weltweit führender Anbieter von JTAG/Boundary Scan Lösungen gemäß IEEE1149.x, stellt unter dem Namen SFX-9305/R ein weiteres I/O Modul im Rahmen seiner Boundary Scan-Hardware-Plattform SCANFLEX® vor.

Das neue Mitglied der Modulfamilie verfügt über fünf Ports zum universellen Test von Schnittstellen, welche per Relais auch komplett …

Systech Europe und XJTAG bieten erweitertes Testen

… eine maximale Abdeckung durch Boundary-Scan-Tests zu erzielen. Die Integration verhilft Testingenieuren zu einer Verkürzung der Testzykluszeiten bei gleichzeitiger Erhöhung der Testabdeckung.

Jörg Lewandowski, Geschäftsführer von Systech Europe, kommentiert die Zusammenarbeit mit XJTAG: „Testingenieure sehen sich mit Komponenten, die wenig oder gar keinen …

GÖPEL electronic forciert LAN-basierende High-Speed Programmierung massiver Flash Images

GÖPEL electronic, weltweit führender Lieferant von JTAG/Boundary-Scan-Systemen, gibt die Markteinführung eines speziellen LAN-Server-Features für die Hardware-Plattform SCANFLEX® bekannt. Die neue Option ermöglicht den Einsatz eines vorkonfektionierten GBit-LAN-Interfaces zum High-Speed Transfer massiver Flash Images bis in den GBit-Bereich zur In-System-Programmierung …

Neues PXI Modul zum Boundary Scan Test von differentiellen I/O

… die Einbeziehung von differentiellen Interfaces in einen Boundary Scan Test.

„Durch das neue Modul sind unsere PXI orientierten Kunden jetzt in der Lage die Testabdeckung von Boundary Scan auch auf den Bereich der differentiellen I/O auszudehnen“ freut sich Thomas Wenzel, Geschäftsführender Gesellschafter der Boundary Scan Division. „Die Kombination …

GÖPEL electronic ermöglicht grafische JTAG/Boundary Scan Projektentwicklung

… Chip-embedded Instruments, In-System Programming und Core Assisted Programming auf einer konsistenten Software-Plattform. Diese mehrdimensionale Instrumentierung bietet den Vorteil der Optimierung von Testabdeckung und Durchsatz durch Definition gemischter Test- und Programmierstrategien.

„Unser Ziel war es, die technologische Leistungsfähigkeit …

GÖPEL electronic portiert VarioTAP® Prozessor-Emulation auf Quorivva Microcontroller von Freescale®

… „Insgesamt profitiert von der neuen Lösung sowohl die Entwicklung durch die Möglichkeit des schnelleren Prototyping, als auch die Produktion in Form von höherer Testabdeckung, verbessertem Testdurchsatz und verringerten Investitionskosten“.

Die Quorivva Mikrocontroller verfügen über eine speziell auf Automotive Applikationen fokusierte Funktionalität …

In-System Emulationstechnik VarioTAP® auf Xilinx® FPGA erweitert

… Boundary Scan Tests, dynamische Emulationstests, Mixed-Signal Tests, sowie Flash Programmierung auf einer Plattform kombiniert werden. Dadurch kann nicht nur die Testabdeckung entscheidend verbessert, sondern auch signifikante Kostensenkungen beim Produktionstest erzielt werden.“

Die beiden neuen VarioTAP® IP-Modelle wurden in enger Kooperation mit der …

Boundary Scan Plattform SCANFLEX® erschließt neue Debug-Interfaces zum Prozessor-Emulationstest

GÖPEL electronic gibt unter dem Namen TIC020 die Entwicklung einer weiteren TAP Interface Card (TIC) im Rahmen der revolutionären JTAG/Boundary Scan Hardwareplattform SCANFLEX® bekannt.

Das neue TIC-Modul verfügt über ein programmierbares Multi-Bus Interface, welches eine fast unbegrenzte Kompatibilität zu einer Vielzahl von standardisierten und proprietären …

Sie lesen gerade: Boundary Scan Modul erweitert strukturelle Testabdeckung auf DDR3 Speicher-Interfaces