(openPR) SUNNYVALE, Kalifornien – 2. November 2009 – MIPS Technologies (Nasdaq: MIPS) stellt eine neue Core-Familie vor, die höchste Leistungsfähigkeit für sehr kostensensitive Embedded-Anwendungen bereitstellt. Darunter fallen 32-Bit-Mikrocontroller (MCUs), Home Entertainment, Personal Entertainment und Home Networking. Die neuen MIPS32®-M14K™- und M14Kc™-Cores sind die ersten MIPS32-kompatiblen Cores, die auch die neue Befehlssatzarchitektur (ISA) microMIPS™ ausführen und dabei eine Leistungsfähigkeit von 1,5 DMIPS/MHz mit einem hohen Grad an Code-Komprimierung erzielen. Die microMIPS ISA erzielt 98% der MIPS32-Performance, reduziert aber gleichzeitig die Codegröße um 35%, was zu erheblichen Einsparungen bei den Halbleiterkosten führt.

Art Swift, Vice President Marketing bei MIPS Technologies erklärt: „Immer mehr Signalverarbeitung und schnellere Datenübertragungsraten erhöhen die Anforderungen an MCUs in vielen kostensensitiven Embedded-Applikationen. Gleichzeitig wird aber eine sehr geringe Stellfläche für die Halbleiterbausteine verlangt. Wir ermöglichen unseren Kunden die Entwicklung hochleistungsfähiger Systeme mit kleinen Formfaktoren – und das zu wesentlich geringeren Entwicklungskosten. Mit der Erweiterung unseres Produktangebots stellen wir MCU- und Systementwicklern äußerst leistungsfähige neue Cores zur Verfügung.“

„MCUs migrieren zunehmend hin zu 32 Bit, um die Anforderungen immer raffinierterer und hochleistungsfähigerer Applikationen zu erfüllen“, so Tony Massimini, Chief of Technology bei Semico Research. „Prozessoren, die 32-Bit-MCUs unterstützen, und andere hochleistungsfähige Embedded-Systeme mit kleiner Stellfläche müssen nicht nur die entsprechende Performance und einen hohen Funktionsumfang aufweisen, sondern auch äußerst kompakt sein, um die Kosten für den Flash-Speicher und andere ICs gering zu halten. Dies ermöglicht eine kleinere Die-Fläche, was eine höhere Integration mit sich bringt. Die Spezifikationen des neuen M14K-Cores bieten alle Voraussetzungen für die nächste Generation dieser Systeme.“

Der M14K-Core für Mikrocontroller

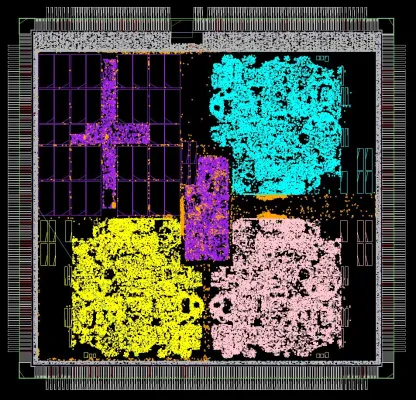

Der M14K-Core bietet für den 32-Bit-MCU-Markt hohe Leistungsfähigkeit und eine fortschrittliche Code-Komprimierung. Bei 130 nm liefert der Core 1,5 DMIPS/MHz und 180 MHz. Der M14K wurde für MCU- und Echtzeit-Embedded-Anwendungen optimiert und bietet eine verringerte Interrupt-Latenzzeit, Flash-Beschleunigung, fortschrittliche Debug-Funktionen wie iFlowTrace™ und Support für AHB Lite als Interconnect-Schnittstelle. Er basiert auf der MIPS32-4K®-Micro-Architektur, die sich bereits in Millionen von SoCs bewährt hat. Der Core ist hochkonfigurierbar und erweiterbar und bietet zahlreiche Implementierungsoptionen, um Kosten zu minimieren und die Wiederverwendbarkeit zu maximieren.

„Microchip freut sich über die fortwährende Innovation und das Engagement von MIPS Technologies im 32-Bit-MCU-Markt“, kommentierte Sumit Mitra, Vice President der High Performance Microcontroller Division bei Microchip Technology. „Die neuen M14K- und M14Kc-Cores sowie die microMIPS ISA bieten Erweiterungen, die für MCU-Anwender von hoher Bedeutung sind. Dazu zählen die weiter verbesserte Interrupt-Latenzzeit und die kleinere Codegröße. Microchip freut sich über die Akzeptanz seiner MIPS-basierten PIC32-MCU-Familie, die branchenweit eine hohe Leistungsfähigkeit bietet. Wie bei unserem 8- und 16-Bit-MCU-Geschäft fühlt sich Microchip auch mit einer langfristigen Roadmap dem MIPS-basierten 32-Bit-MCU-Angebot verpflichtet.“

Der M14Kc-Core für hochleistungsfähige Anwendungen mit geringer Stellfläche

Der M14Kc-Core basiert auf dem M14K-Core und bietet zusätzliche Leistungsmerkmale für Embedded-Anwendungen in den Bereichen Home Entertainment, Home Networking und Personal Mobile Entertainment. Diese Applikationen erfordern eine kompakte Bauweise aber auch die Möglichkeit, zunehmend komplexe Software-Algorithmen auf einem RTOS oder Linux auszuführen. Auf der Basis der MIPS32-4KEc™-Micro-Architektur, die mit Linux und einer Java Engine ausgestattet ist und hohe Performance für die Android-Plattform bereitstellt, weist der M14Kc-Core einen kompletten Cache-Controller und eine Translation Lookaside Buffer (TLB) Memory Management Unit (MMU) auf.

microMIPS ISA für fortschrittliche Code-Komprimierung

Die Grundlage der M14K- und M14Kc-Cores bildet die neue microMIPS ISA, die für die meisten Befehle 32-Bit-Performance mit 16-Bit-Codegröße ermöglicht. Die microMIPS ISA kombiniert umverschlüsselte und neue 16- und 32-Bit-Befehle, um ein ideales Gleichgewicht zwischen Leistungsfähigkeit und Codedichte zu erzielen. Sie enthält alle MIPS32-Befehle und applikationsspezifischen Erweiterungen (ASEs), einschließlich MIPS-3D® ASE, MIPS DSP ASE, MIPS MT ASE und SmartMIPS® ASE, sowie neue Befehle zur Reduzierung der Codegröße. Die microMIPS ISA ist rückwärtskompatibel, was die Wiederverwendung einer optimierten MIPS-Micro-Architektur ermöglicht. Mit kleineren Speicherzugriffen und einer effizienten Nutzung des Befehls-Cache, trägt die microMIPS ISA auch dazu bei, die Stromaufnahme des Systems zu verringern.

Ecosystem und Tool-Support

MIPS Technologies bietet auch umfassenden Softwareentwicklungstool-Support für die neuen Cores: Die Eclipse-basierte MIPS Navigator™ Integrated Component Suite (ICS) und die System Navigator™ Probes für das Debugging. MIPS Technologies arbeitet auch mit führenden Drittanbietern in den Bereichen Software-, Tool- und OS-Support zusammen.

Simulations-Support

MIPS bietet auch genaue und schnelle Simulationsmodelle für die M14K- und M14Kc-Cores. SoC-Entwickler können somit 100% zyklusgenaue Modelle nutzen, die mit der Technologie von Carbon Design Systems entwickelt wurden. Damit sind eine Verifikation in SystemC sowie Co-Simulationsumgebungen möglich. Softwareentwickler können zudem schnelle Befehlssatzsimulatoren nutzen, die gemeinsam mit Imperas entwickelt wurden und in Softwareentwicklungs- sowie virtuellen Plattformen zum Einsatz kommen.

Verfügbarkeit

Die neuen M14K- und M14Kc-Cores stehen im ersten Quartal 2010 zur Verfügung. Weitere Information unter:

MIPS, MIPS32, MIPS64, iFlowTrace, microMIPS, M14K, M14Kc, 4K, 4KEc, SmartMIPS, MIPS-3D und MIPS-Based sind Marken von MIPS Technologies , Inc. in den USA und in anderen Ländern. Alle anderen hier erwähnten Marken sind im Besitz der jeweiligen Eigentümer.