(openPR) Entwickler von HF-, MEMS- und Sensor-Bauteilen benötigen schnell umsetzbare Lösungen zum Herstellen von SMT-montierbaren QFNs mit offenem Gehäuse ("Open Package" oder "Air Cavity"). Der traditionelle Weg ein solches Gehäuse herzustellen benötigt ein entsprechendes Prägewerkzeug oder aufwändiges chemisches Ätzen eines Leadframes und teures Aufbringen einer Vergussmasse, um die Außenkonturen zu definieren. Andere gebräuchliche Verfahren solch ein offenes Gehäuse aufzubauen basieren auf Dick- oder Dünnfilmtechniken in Verbindung mit Keramik-Substraten. All diese eben genannten Aufbau-Technologien von Open Packages benötigen monatelange Entwicklungs- und Herstellungszeiten, und die daraus resultierenden Kosten sind nur für große Fertigungsstückzahlen tragbar. Während der letzten 10 Jahre wurden die meisten Massenproduktionen nach Südostasien oder China verlagert, und die in Europa und Nordamerika verbliebenen Applikationen beschränken sich auf "High Mix und Low Volume". Die meisten Produkte hierzulande laufen also nur noch in kleinen Stückzahlen.

MirrorSemiconductor entwickelte nun ein neues Verfahren, um für "High-Mix Low-Volume"-Produktionen drahtbondbare, offene Halbleitergehäuse schnell und kostengünstig herzustellen. Diese neue Herstellungsmethode basiert auf 2-lagigen organischen Substraten, welche bevorzugt zur Herstellung üblicher PC-Baugruppen eingesetzt werden. Lange Wartezeiten, um aus Kupfer ein Leadframe herzustellen, oder hohe Kosten zum Aufbau eines Keramik-Substrats entfallen damit. Die einsetzbaren organischen Substrate bestehen aus BT (Bismaleimid-Triazin), PTFE (Polytetra-fluoräthylen). LCP (Flüssigkristall-Polymer) und Polyamid. Für manche Anwendungen kann sogar FR-4 eingesetzt werden. Ständig kommen auch neue Verbundstoffe mit immer besseren HF-Eigenschaften auf den Markt. Die meisten Leiterplatten-Anbieter, deren Produkte auch für anspruchsvolle Mikrowellen- und HF-Produkte geeignet sind, sind auch in der Lage, für Halbleiter geeignete Substrate für Air-Cavity-Packages herzustellen. Substrate für drahtbondbare offene QFN-Gehäuse müssen in der Regel nur zweilagig ausgeführt sein.

Es ist nun wichtig die Vorteile und Grenzen abzuwägen, wenn mit Standardprozessen, zur Herstellung von gewöhnlichen Leiterplatten auch Substrate für hochfrequenz- und halbleitergeeignete, organische, offene Gehäuse hergestellt werden sollen. Auch Designer-Regeln müssen definiert werden, um für typische "High-Mix Low-Volume"-Anwender eine breite Palette verschiedener offener QFN-Gehäuse schnell verfügbar zu machen.

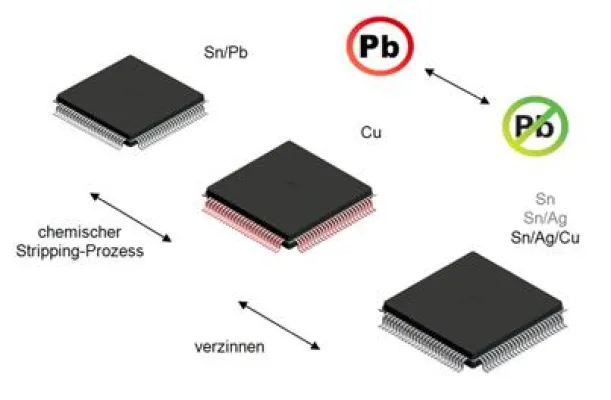

Um ein marktgerechtes Produkt zu entwickeln, wurden hierzu folgende Vorgaben festgelegt: Die JEDEC-Normen für quadratische und rechteckige QFNs (3 mm bis 12 mm) sollen eingehalten werden. Der Anzahl der Anschlüsse sollte sich zwischen 4 und 100 bewegen und im typischen QFN- (vierseitig) oder DFN-Muster (zweiseitig) angeordnet sein. Standard sind einreihige Versionen, optional sollen aber auch zweireihige Versionen möglich sein. Die üblichen Pin-Abstände von 0,4 mm, 0,5 mm, 0,65 mm, 0,8 mm, 1,0 mm und 1,27 mm sollen eingehalten werden, dennoch sollten nach Kundenwunsch auch Abweichungen von diesen Standard-Geometrien zulässig sein. Silizium-Dies, MEMS, Sensoren und auch LED-Dies sollen mit herkömmlichen, silberhaltigen Epoxid-Klebern montiert werden können. Auch eutektisches Löten metallbeschichteter Dies soll möglich sein. Zum Bonden der Dies sollen normale Gold- oder Aluminiumdrähte (25 - 33 µm) oder Flachbänder verwendet werden können. Das fertige Gehäuse muss im normalen SMD-Prozess, bleihaltig oder bleifrei, auf eine Leiterplatte gelötet werden können oder auf einen Testsockel steckbar sein. Die notwendige Fertigungstechnologie für diese Packages sollte geeignet sein, Stückzahlen von 100-500 ohne nennenswerte Werkzeug¬kosten herzustellen.

Zusammenstellung der wichtigsten Anforderungen

• Offenes Gehäuse

• Möglichkeit zum Drahtbonden innerhalb des Gehäuses

• SMT-Montage auf Leiterplatten

• bleifrei (RoHS-konform)

• Sehr gute HF-Eigenschaften

• Organische Basismaterialien

• Schnelle Fertigung beim lokalen Leiterplatten-Hersteller

• Sehr niedrige Werkzeugkosten

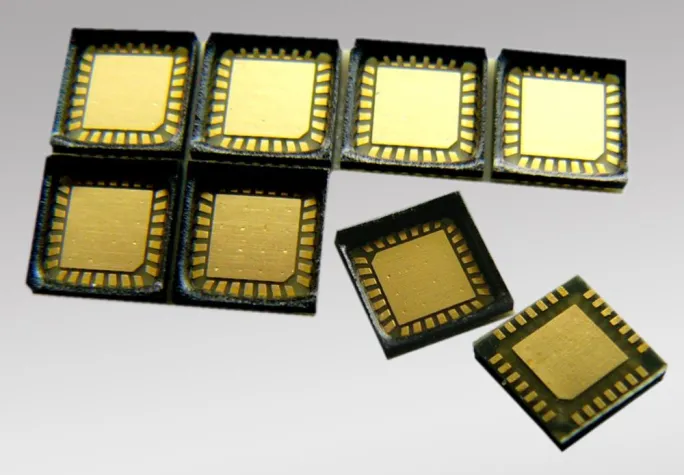

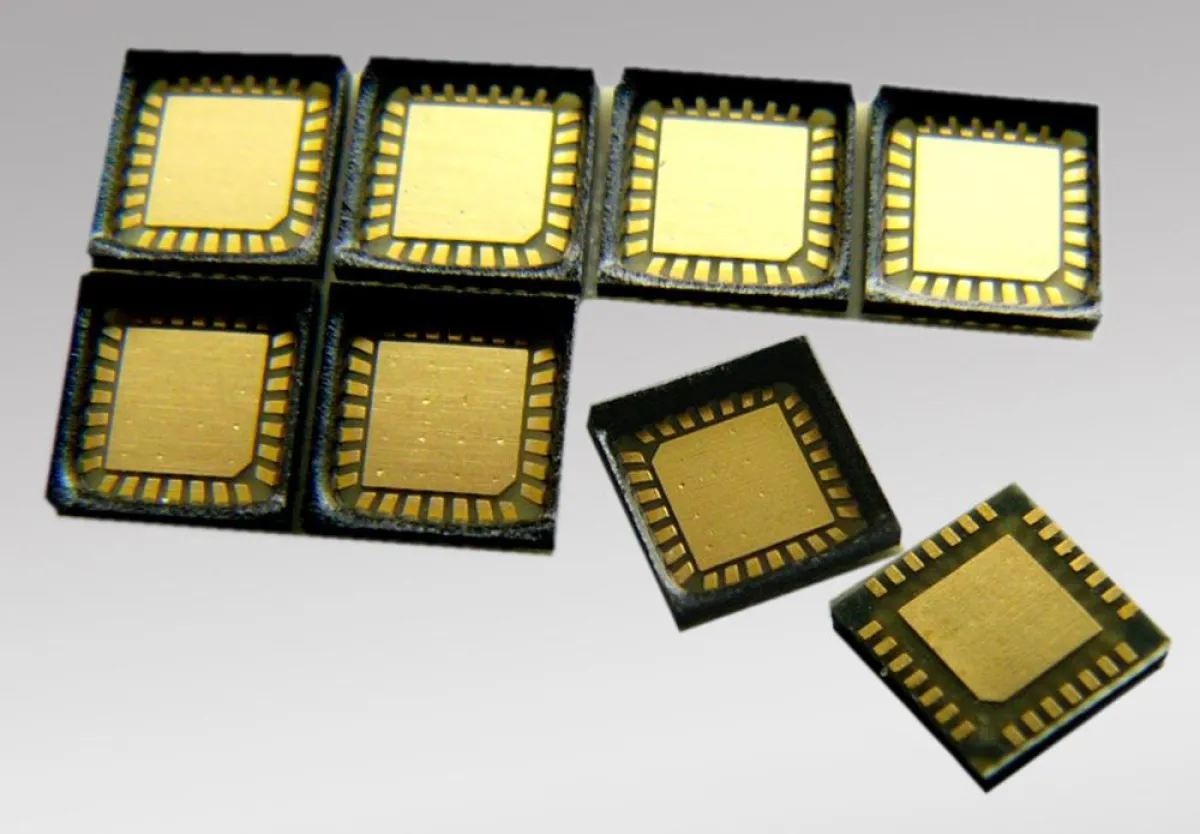

Mittlerweile sind im Lieferprogramm bereits 31 Gehäusetypen in 9 Standardabmessungen, mit 18 verschiedenen Pin-Anzahlen und in 4 verschiedenen Pin-Abständen enthalten, die alle nach diesen Design-Vorgaben aufgebaut wurden. Das Basismaterial besteht immer aus einem Laminat-Kern mit 2 durchkontaktierten Kupfer-Layern. Zwei Materialtypen stehen hierfür zur Auswahl: Der erste besteht aus BT (Bismaleimid-Triazin, Typ HL832NS) der Firma Mitsubishi Gas and Chemical aus Japan, der andere aus RO4003C der Firma Rogers Corporation aus USA. BT ist allgemein sehr verbreitet bei der Herstellung von BGAs, RO4003C findet sich häufig in Mikrowellen-Applikationen.

Die ideale Substrat-Stärke für BT und RO4003C beträgt 200 µm. Übliche Leadframes für QFNs messen ebenfalls 200 µm. Die Dicke der Kupferkaschierung beträgt jeweils 12 bis 18 µm bevor die Nickel- und Gold-Beschichtung aufgebracht wird. Bei der Verwendung dickeren Basismaterials würden die Vias im Durchmesser zu breit; dünnere Substrate könnte man fertigen (z.B. 150 µm), jedoch wären diese für eine praktische Handhabung zu empfindlich.

Um eine gute Bondfähigkeit mit üblichem 25 µm Golddraht sicherzustellen, ist die Innenseite des Gehäuses (Oberseite des Substrats) mit mindestens 3,8 µm Nickel und 1,3 µm Gold beschichtet. Für gute Bonds ist eine Reinheit des Goldes von 99,999% (auch als "Soft-Gold" bezeichnet) erforderlich. Die Unterseite des Gehäuses ist für den SMT-Lötprozess optimiert, um die hierbei auftretenden typischen Effekte wie Gold-Versprödung oder "Black-Pads" zu minimieren. Hierfür wird die untere Kupferlage mit 3,8 µm und 0,127 µm chemisch Nickel/Gold (auch ENIG oder "Flash Gold" genannt) veredelt.

Falls die Applikation des Kunden Aluminium-Bonds vorsieht, kann auch im Inneren des Gehäuses mit einer ENIG-Beschichtung gearbeitet werden.

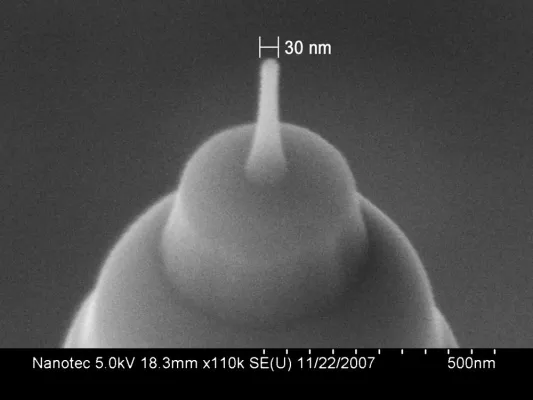

Der Durchmesser der beschichteten Vias beträgt 0,127 - 0,152 mm. Die Wandstärke der Vias misst 20 - 25 µm. Die Vias werden entweder mit leitendem oder nicht-leitendem Material verschlossen (gepluggtes "Via in Pad"), an den Oberflächen abgeschliffen und abschließend mit einer Nickel/Gold-Schicht überzogen. Die Vias sind somit visuell nur schwer zu erkennen. Die Vias sind über das gesamte Die-Pad gleichmäßig in Abständen von 0,8 - 1,27 mm verteilt. Für manche Mikrowellenapplikationen ist es erforderlich eine EMV-Simulation mit Softwarepaketen wie Ansoft oder CST durchzuführen, um störende Resonanzen auszuschließen und eine optimale Verteilung der Vias im Die-Pad zu definieren.

Zum Aufbau der Seitenwände des Gehäuses gibt es zwei Möglichkeiten: Zum Einen wird flüssige Epoxid-Vergussmasse, wie Henkel FP4451D, mittels Dosiernadel aufgetragen. Um hierbei beste Ergebnisse zu erzielen, werden vollautomatische Dispenser verwendet. Die Höhe der Seitenwände kann je nach Vorgabe zwischen 0,65 und 1,0 mm betragen. Nach dem Aushärten der Vergussmasse und der so entstandenen Gehäuseumrandungen wird das Substrat in einzelne die Gehäuse geteilt. Hierzu wird eine Wafersäge eingesetzt, wie sie normalerweise in der Halbleiterfertigung verwendet wird. Nach dem Vereinzeln beträgt die Wandstärke der Open Packages ca. 0,30 - 0,75 mm. Das Aufbringen und Bearbeiten der Umrandung erfordert eine sehr hohe Genauigkeit, damit die Vergussmasse am Ende nicht die Bond-Pads bedecken. Die Oberseite der so aufgebrachten Umrandung ist allerdings nicht sonderlich eben. Diese bewegt sich in einem Toleranzbereich von 30 - 50 µm, was zu Problemen führen kann, wenn das Gehäuse zum Schluss noch mit einem Lid verdeckelt werden soll. Bei der zweiten Methode wird zum Aufbringen der Umrandung eine Schablone für die Vergussmasse angefertigt. Dieses Verfahren hat deutliche Vorteile. So benötigt man durch die präzise gegossene Umrandung auch eine exakt definierbare Menge von Vergussmasse, wenn das Gehäuse nach Fertigstellung komplett verschlossen werden soll, was zu einer sehr ebenen Bauteil-Oberfläche führt. Auch das Aufbringen eines Deckels wird durch die glatte Oberseite der Umrandung vereinfacht.

Die gesamte Bearbeitung wird idealerweise als "Step-and-Repeat" ausgeführt, um die vorgegebene Substrat-Geometrie optimal ausnutzen zu können. Die einzelnen QFNs auf dem Substrat sind durch 0,254 mm breite Gassen voneinander abgesetzt. Markierungen in den Kupferlagen, an den Rändern des Substrat-Arrays, dienen als Referenzmarken zum präzisen Sägen. Fanglöcher zum Fixieren können auf Wunsch ebenfalls angebracht werden. Die QFNs können aber auch bereits vor der weiteren Verarbeitung vom Substrat abgetrennt werden, um Einzelstücke herzustellen zu können. Alternativ können die Substarte auch nur angesägt werden, sodass zum Vereinzeln nach dem Bonden lediglich ein Skalpell, aber keine weiteren aufwändigen Maschinen mehr verwendet werden müssen (sh. Bild).

MirrorSemiconductor bietet mit dieser Idee schnell verfügbare QFN-Gehäuse, die auch anspruchsvollen Anforderungen aus den Bereichen HF, MEMS und Sensorik gerecht werden. Die ideale Stückzahl für diese Art von Gehäusen liegt bei 100 - 500 Stück. Allerdings sind kleine Abweichungen in Performance und Bearbeitbarkeit bei organischen Laminaten nicht ganz auszuschließen. Auch gibt es Unterschiede bei verschiedenen Leiterplattenlieferanten, abhängig von deren Erfahrungen auf den Gebieten HF-Elektronik und Mikrowellentechnik sowie den eingesetzten Produktions-anlagen. MirrorSemiconductor ist weiterhin am Forschen mit anderen Materialien und Fertigungsmethoden, um künftig auch Produkte für noch höhere Frequenzbereiche anbieten zu können.

Im deutschsprachigen Raum wird die Firma MirrorSemiconductor von der Factronix GmbH in Alling bei München vertreten.

www.mirrorsemi.com

www.factronix.com

Productronica 2009 Halle A2 / Stand 454