(openPR) Freiburg, 26. Mai 2021 – Die PLC2 Design GmbH bringt mit der L5 (De-) Compression IP eine Bildkompressions-IP für FPGAs auf den Markt. L5 bezeichnet die Haupteigenschaften und Vorteile der IP: Lightweight, Low Latency, Low Power und Lossless. Die L5 ist mit Xilinx AXI-Streaming-Schnittstellen ausgestattet und lässt sich nahtlos in bestehende Bildverarbeitungsanwendungen integrieren.

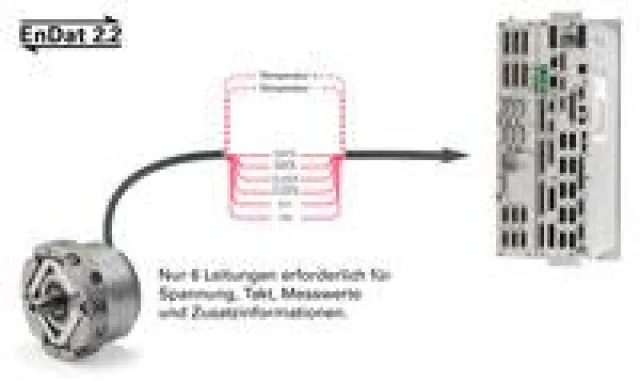

Mit der PLC2 L5 (De-) Compression IP können Anwender modernste Sub-Frame-Latency in Kombination mit geringem Stromverbrauch und einer leichtgewichtigen Implementierung bezüglich Ressourcenverbrauch und verlustfreier Dekompression erreichen – und das für eine Vielzahl von Anwendungen auf Edge Devices und in der Cloud. Die Integration in bestehende Systeme ist sowohl für die Datenübertragung mit anschließender Dekompression, als auch für die Speicherung von komprimierten Daten mit existierender Hardware möglich.

Die Use Cases für die L5 (De-) Compression IP sind kamerabasierte Anwendungen in der Automobilindustrie (inklusive schwerer Lkw und Nutzfahrzeuge), Bahnanwendungen, Roboter, Drohnen und Weitere. Mit einer Datenreduzierung von bis zu 60 % wird Raum geschaffen für z.B. die zukünftige Nutzung höher auflösender Sensoren.

Stefan Krassin, Geschäftsführer der PLC2 Design GmbH, führt aus:

"Ich bin überzeugt von unserer brandneuen Kompressions-IP. Unserem breiten Kundenspektrum weltweit bietet die L5 einen erheblichen Mehrwert. Wir liefern mit der L5 maximale Kompression bei sehr geringem Platzbedarf und geringen Stromkosten.“

Willard Tu, Senior Director of Automotive bei Xilinx, erklärt:

"Wir freuen uns sehr über die Zusammenarbeit mit PLC2 und die Bereitstellung von Xilinx AXI-Streaming-Schnittstellen, die einfach in Bildverarbeitungsanwendungen integriert werden können. Durch den Einsatz der Xilinx-Technologie kann PLC2 seinen Kunden in der Automobilbranche nun eine ausgefeilte Funktionalität und einen noch größeren Nutzen bieten. Bei der Komprimierung von Videos, die während der ADAS-Datenerfassung aufgenommen werden, können bis zu 60 % Speicherplatz eingespart werden."

Weitere Information unter: https://www.plc2.com/l5